Nios2 simulator

Nios2 simulator

| Library: | System On Chip components |

| Introduced: | 3.2 |

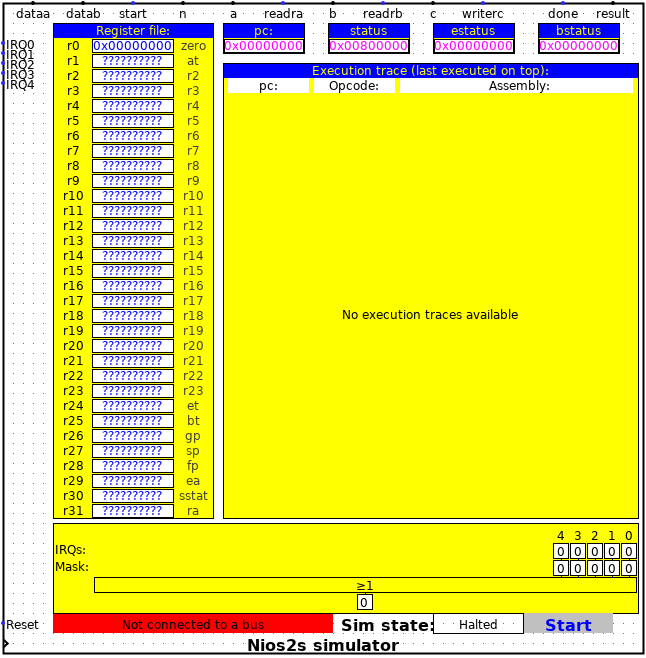

| Appearance: |

|

Behavior

The nios2 simulator is a complete ISA-simulator of Intel's nios2 soft core (except for the f-version). It can be used to show the execution of a program on an embedded system. Note that although the simulator executes one instruction per clock cycle, it is not a cycle accurate simulation as aspects like cache-stalls, data-dependency stalls, bus wait cycles, etc. are not taken into account in the simulation. It provides a functional simulation for showing SOC-design where the hardware is not yet available.

Pins

On the north side of the Nios2 simulation component you will find the custom-instruction interface signals where you can add your custom-instruction hardware/accelerators to be used in your simulations. Please refer to Intel's documentation on custom instructions with the nios2 on how to use them.

On the west side of the Nios2 simulation components following inputs are present:

- Reset: This the reset input of the Nios2 simulation component that will reset asynchronously the Nios2 when at '1' and let the cpu run when at '0'.

- Clock: This is the clock input of the Nios2 simulator component. Each time a positive edge is seen on this input a new instruction will be fetched and executed.

- IRQ[0..31]: The Nios2 simulator provides up to 32 IRQ inputs (defined by the below described attribute IRQs). Each of these IRQ-inputs is active high. Please refer to Intel's documentation on IRQ-behavior on how to provide proper signals to these inputs.

Attributes

The Nios2 simulation component provides following attributes:

- Reset vector: This attribute specifies the memory address of the first instruction to be executed when the Reset pin is activated. In general the value specified here should be the address of the entry point of your program. Note that all addresses are 32-bit values.

- Exception vector: Upon detection of an IRQ (see IRQ-pins above), or an software exception instruction, the Nios2 simulator will start executing the program starting from this address. In general the value specified here should be the address of the exception handling routine in your program.

- Break vector: This attribute specifies the memory address of the break service routine which is executed upon detection of a break instruction.

- Number of IRQ lines: This attribute specifies how many external IRQ-pins are available. It's value can be within 0 (no IRQ lines) and 32 (maximum number of IRQ lines).

- State visible:When disabling the state by specifying No for this attribute the simulation speed can be improved (see the remark on simulation speed in the library description).

- Label: Here the label of the components can be specified. Note that the label is used in many places to reference to this component. In case the label is not defined the components will be referenced as "Nios2s simulator @x,y" where x and y are the absolute coordinates of the anchor of this component inside the sheet.

- Label font: With this attribute the font of the label can be specified.

- Label visible: With this attribute you can specify if the label is visible or not.

- Connected Bus: This attribute let's you connect the Nios2 simulator to a bus component. For a successful simulation you have to connect your Nios2 simulator to such a component.

Visible components

The Nios2 simulator has several state components that are visible when the State visible attribute is set to True. Most of these components can also be visualized in a separate window when the component is hidden in a sub-circuit (see super-component menu below). The different components are:

- The register file. The Nios2 processor contains 32 general purpose registers (r0..r31). The current values of these registers are shown on the left-top square marked by Register file. When a register value is shown by a sequence of question marks, it means that the value is unknown (normal start-up behavior of the processor). Each time a value is written to a register it will be highlighted in blue and the new value will be shown.

- The program counter. The program counter (PC) hold the current address from which the next instruction will be fetched.

- The status register. The status register (status) hold the current state of the Nios2 processor. For information on the status register please refer to Intel's documentation on the nios2 processor.

- The exception status register. The exception status register (estatus) holds a copy of the status register when entering an exception. For information on the estatus register please refer to Intel's documentation on the nios2 processor.

- The break status register. The break status register (bstatus) holds a copy of the status register when a break instruction is executed. For information on the bstatus register please refer to Intel's documentation on the nios2 processor.

- The execution trace window. The execution trace window shows the last 21 instructions executed by the nios2 processor. The last instruction executed is shown on the top. The tace window provides three parts of information, namely:

- The program counter value where the instruction was fetched.

- The binary opcode of the fetched instruction.

- The assembly mnemonic of the fetched instruction in case the fetched instruction has a correct binary opcode.

- The IRQ-status, irq-mask, and irq-pending display. In case at least one IRQ-input is selected by the Number of IRQ lines attribute, this component will be shown. For each of the IRQ-pins a square on the top of the component will indicate the current state of the IRQ-line. The square below will indicate the corresponding bit in the IRQ-mask register. Finally the square on the bottom will indicate if an unmasked IRQ is pending. Note: this component does not show the state of the global IRQ-enable bit which is present in the status register.

- The connected bus indicator. To the bottom left of the component (shown above in red) is the indicator to which bus component the nios2 is connected. In case the nios2 is connected to a bus component, this indicator will turn green and shows the label of the connected bus. This bus indicator is not available in the separate window view and will not be hidden by the State visible attribute.

- The simulation control component. To the right of the connected bus indicator you can find the simulation control component. This component is described in more details here, and is available as dynamic element.

Dynamic elements

The Nios2 simulation components provides the soc simulation controller as dynamic component.

Menu items

Clicking with the right mouse button on the symbol of the Nios2 simulator will pop-up a menu. This menu is extended with three new menu items, namely:

- Open assembler. Selecting this menu item will open the assembler. The assembler provides the possibility to write your own assembly programs and run them on the Nios2.

- Read elf file. Selecting this menu item will open a file selection window in which you can read in an elf-file (executable) generated for a Nios2 processor by for example a gcc-cross compile tool chain. The executable contents of the elf-file will be loaded into memory, the reset vector of the Nios2 will be set to the entry-point of the loaded program, and the Nios2 simulator will be initialized to reset state. Note that loading an elf program will not modify the value of the Reset vector attribute.

- Show loaded program. This menu option is only present if an executable program has been loaded into memory, either by the assembler, or by reading an elf file. When selecting this menu item the disassembler will be shown.

Super circuit menu items

When the Nios2 simulator is located in a sub-circuit, it will add four menu items to the menu of this sub-circuit, namely:

- <name>: Open assembler. Selecting this menu item will open the assembler. The assembler provides the possibility to write your own assembly programs and run them on the Nios2.

- <name>: Read elf file. Selecting this menu item will open a file selection window in which you can read in an elf-file (executable) generated for a Nios2 processor by for example a gcc-cross compile tool chain. The executable contents of the elf-file will be loaded into memory, the reset vector of the Nios2 will be set to the entry-point of the loaded program, and the Nios2 simulator will be initialized to reset state. Note that loading an elf program will not modify the value of the Reset vector attribute.

- <name>: Show CPU State. This menu item will open a new window showing the visible component 1 through 7 as described in the Visible components section.

- <name>: Show loaded program. This menu option is only present if an executable program has been loaded into memory, either by the assembler, or by reading an elf file. When selecting this menu item the disassembler will be shown.

In the above menu items <name> is the label of the Nios2 simulator (see the Label attribute above). If no label name is given <name> is given by Nios2@x,y where x and y are the coordinates of the anchor position of the Nios2 Simulator in the sub-circuit.

Supported instructions

| Arithmetic and logical instructions | |||||

| and | or | xor | nor | sub | mul |

| div | divu | mulxss | mulxuu | mulxsu | andi |

| ori | xori | andhi | orhi | xorhi | addi |

| subi | muli | nop | mov | movhi | movi |

| movui | movia |

|

|||

| Comparison instructions | |||||

| cmpeq | cmpne | cmpge | cmpgeu | cmplt | cmpltu |

| cmpgt | cmpgtu | cmple | cmpleu | cmpeqi | cmpnei |

| cmpgei | cmpgeui | cmplti | cmpltui | cmpgti | cmpgtui |

| cmplei | cmpleui |

|

|||

| Custom instructions | |||||

| custom |

|

||||

| Data transfer instructions | |||||

| ldw | ldh | ldhu | ldb | ldbu | ldwio |

| ldhio | ldhuio | ldbio | ldbuio | stw | sth |

| stb | stwio | sthio | stbio |

|

|

| Other control instructions | |||||

| trap | eret | break | bret | rdctl | wrctl |

| flushd | flushda | flushi | initd | initda | initi |

| flushp | sync |

|

|||

| Program control instructions | |||||

| callr | ret | jmp | call | jmpi | br |

| bge | bgeu | blt | bltu | beq | bne |

| bgt | bgtu | ble | bleu |

|

|

| Shift and rotate instructions | |||||

| rol | ror | sll | sra | srl | roli |

| slli | srai | srli |

|

||

Implemented control registers

| Register | Name | Remarks |

| 0 | status | Only RSIE constant at 1 and PIE |

| 1 | estatus |

|

| 2 | bstatus |

|

| 3 | ienable | Number of bits depends on Number of IRQ lines attribute. |

| 4 | ipending | Number of bits depends on Number of IRQ lines attribute. |