门延迟

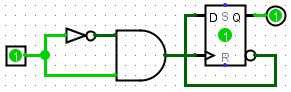

作为 Logisim-evolution 算法复杂程度的示例,请考虑以下电路。

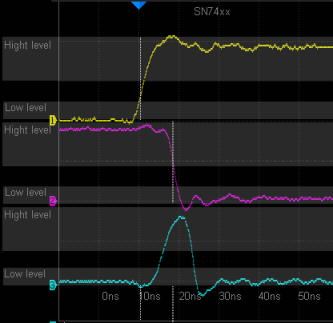

这“显然”总是输出 0。但 NOT 门在现实中不会对其输入立即做出反应,在 Logisim 中也不会。 因此,当该电路的输入从 0 变为 1 时,与门将短暂看到两个 1 输入,并短暂发出 1。 您不会在屏幕上看到它。 但当我们使用与门的输出作为 D 触发器时钟的输入时,效果是可以观察到的。

将 0 输入变为 1 会导致瞬时 1 进入 D 触发器,因此每次电路输入从 0 变为 1 时,触发器的值都会切换。还可以通过以下方式观察详细的序列: step-by-step 模拟模式。

每个组件都有与之相关的延迟。 Logisim-evolution 中内置的更复杂的组件往往具有更大的延迟,但这些延迟有些随意,可能无法反映现实。

Logisim world

Real world

从技术角度来看,在单个电路中处理这种复杂程度相对容易。 然而,处理跨子电路的门延迟要复杂一些。 Logisim-evolution 确实尝试通过将所有原始组件的传播值放入单个调度中来正确解决此问题,而不管组件位于哪个子电路中。

通过 项目选项 窗口的 模拟选项卡 ,您可以 配置 Logisim-evolution 为组件的传播添加随机、偶尔的延迟。 这是为了模拟真实电路的不均匀性。 特别是,使用两个 NOR 门构建的 R-S 锁存器将在没有这种随机性的情况下振荡,因为两个门将同步处理其输入。 默认情况下禁用此随机性。

请注意,我并没有说 Logisim-evolution 总是能很好地解决门延迟问题。 但至少它尝试过。

下一步: 振荡错误 。